# Project Final Report: Bread Proofing Box

Team 3

Caleb Williamson

Ellias Palcu

Aaron Young

December 1, 2016

# Contents

| 1 | Introduction                                                                                   | 1                                           |

|---|------------------------------------------------------------------------------------------------|---------------------------------------------|

| 2 | Requirements                                                                                   | 1                                           |

| 3 | Method3.1 Component List3.2 System Input3.3 System Control3.4 System Output3.5 System Analysis | 2<br>2<br>3<br>3<br>3                       |

| 4 | Design 4.1 Architecture Design                                                                 | 4<br>4<br>5<br>5                            |

| 5 | Division of Labor                                                                              | 7                                           |

| 6 | Design Flow and Verification Strategy                                                          | 8                                           |

| 7 | Verification and Testing 7.1 Proofing State Machine                                            | 9<br>11<br>12<br>13<br>14<br>14<br>14<br>16 |

| 8 | 8.1 Bread Proofing Box                                                                         | 16<br>17<br>18<br>22<br>25                  |

| 9 | Future Work         9.1 Improvements                                                           | 30<br>30<br>31<br>31<br>31<br>32            |

| 10 Conclusion                                 |  |           |  |  |  |  |

|-----------------------------------------------|--|-----------|--|--|--|--|

| Appendices                                    |  |           |  |  |  |  |

| Appendix A VHDL Source Code                   |  | 33        |  |  |  |  |

| A.1 Bread Box Top-level                       |  | 33        |  |  |  |  |

| A.2 Proofing State Machine                    |  | 47        |  |  |  |  |

| A.3 Output Control Module                     |  | 64        |  |  |  |  |

| Appendix B Testbench VHDL Code                |  | 67        |  |  |  |  |

| B.1 Proofing State Machine Test Bench         |  | 67        |  |  |  |  |

| B.2 Output Control Module                     |  | 72        |  |  |  |  |

| Appendix C Web Interface Source Code          |  | <b>74</b> |  |  |  |  |

| C.1 Web Interface Top-Level                   |  | 74        |  |  |  |  |

| C.2 Web Interface Database Code               |  | 80        |  |  |  |  |

| Appendix D Recipe—Extra-Tangy Sourdough Bread |  | 83        |  |  |  |  |

### 1 Introduction

Bread making is as much an art as a science. There are many factors at work to determine how the final loaf will turn out. These variables include the activity of the starter, the water to-flour-ratio, and the time and temperatures for the various fermenting, proofing, and rising stages. The goal of this project is to add more science to the art of bread fermenting by creating an advanced, FPGA controlled, bread proofing box. This bread proofing box will allow precise control over the time, temperature, and humidity during the fermenting and rising stages. This fine control over the fermenting conditions will allow for experiments to be setup to determine the effects that temperature and humidity have on the final loaf of bread.

Upon accomplishing the basic functionality of allowing precise control and conclusive experimentation, several augmentations will be included in the final design. These augmentations include extending the availability of the data by displaying current and prior data though a web interface at real-time, minute resolution. By experimenting with different temperature and humidity conditions, the bread can take on many different characteristics. Through storing these characteristics in a database, users can view previous proofing runs and any min/max and average conditions experienced. Ultimately, in accessing this data, users may extend their control by analytically making statistic conclusions to determine optimal bread proofing conditions. Once the optional conditions are discovered, the box should be able to be used to produce consistently delicious bread.

# 2 Requirements

All of the requirements are working towards the final goal of creating an experiential bread proofing box that will allow experimenting with the effects temperature, humidity, and time have on bread making.

#### Primary Goals:

- 1. Monitor Temperature of Box.

- 2. Monitor Humidity of Box.

- 3. Adjust Humidity and Temperature.

- 4. Timer for rising time.

- 5. Alarm for rising done.

- 6. LCD interface for button control.

#### Stretch Goals:

- 1. Web interface/app for real-time, remote monitoring and control.

- 2. Database to store previous proofing stages.

- 3. Monitoring system to check bread rising via ultrasound.

# 3 Method

This project can be subdivided into four major aspects: input, control, output, and analysis. The system will use the control logic to make decisions based upon the input provided to it, and those decisions will affect the output of the system over time.

### 3.1 Component List

The components used to build the bread box are listed in Table 1.

| Item                            | Specific Part                                     |    | Price |  |

|---------------------------------|---------------------------------------------------|----|-------|--|

| Humidity and Temperature Sensor | HIH6130                                           | \$ | 29.95 |  |

| Ultrasonic Sensor               | HC-SR04                                           | \$ | 3.95  |  |

| Keypad                          | PmodKYPD                                          | \$ | 9.99  |  |

| Time Keeping                    | PmodRTCC                                          | \$ | 8.99  |  |

| Pin out                         | PmodCON1                                          | \$ | 4.99  |  |

| Voltage level converter         | SparkFun Logic Level Converter<br>Bi- Directional | \$ | 2.95  |  |

| Relay module                    | SunFounder2 Channel                               | \$ | 6.79  |  |

| Piezo Buzzer                    | PS1240                                            | \$ | 1.50  |  |

| Humidifier                      | HealthSmart Tabletop Humidifier <sup>1</sup>      | \$ | 15.00 |  |

| Light bulb for Heat             | 125 watt incandescent heat lamp bulb              | \$ | 4.97  |  |

| Light socket                    | Bayco 8.5" Clamp Light                            | \$ | 6.47  |  |

| Enclosure walls                 | Foam Board                                        | \$ | 5.31  |  |

| Enclosure Window                | 18" X 42" Impact Acrylic                          | \$ | 11.97 |  |

| Humidifier Connecting Tube      | Foil Dryer Duct                                   | \$ | 9.97  |  |

Table 1: Parts List

# 3.2 System Input

The system needs to accept programming input directly from the user as well as take sensor input from the sensors. The user must be able to input timing, temperature, and humidity settings using a keypad on the device. The humidity and temperature sensor must also send its input to the FPGA for processing. Finally, an ultrasonic sensor may potentially be used to monitor the rising state of the bread in future work. Figure 1 shows the particular temperature and humidity sensor, the keypad, and the ultrasonic sensor that were selected for this project.

<sup>&</sup>lt;sup>1</sup>Obtained on clearance do to broken/missing top redirector. Originally \$64.31.

Figure 1: Temperature and humidity sensor HIH6130, keypad pmodKYPD, and ultrasonic sensor HC-SR04.

### 3.3 System Control

The control logic initially processes the inputs from the user and sets up the system environment as required. Throughout the proofing process, this control logic continues to make temperature and humidity decisions based upon the sensor input provided, as well as the initial configuration that was set up by the user. The user input specifies multiple time points and the desired temperature/humidity at those corresponding time points. The controller stores this input and uses this data to maintain the temperature and humidity between the bread rising stages. The LCD screen and web interface are used to display the current stage and time remaining for that phase.

# 3.4 System Output

There are two types of output from the system. One type of output is an audible alert to let the user know that the proofing process is complete. The alarm will sound to let the user know that the bread is ready for the next step. The second kind of output involves manipulating the temperature and humidity of the enclosure via the heat lamp and the humidifier.

# 3.5 System Analysis

By developing a web interface, the temperature and humidity progression through time within the bread proofing box can be graphically analyzed. By being able to view temperature and humidity values graphically, users can compare final bread results with their specified set points. Furthermore, in having access to these chart analyses, a better understanding can be developed in how temperature and humidity impact one another. To

accomplish this, data would not only have to be graphed on at a fine-grained resolution, but must be stored to allow for further review, if necessary.

# 4 Design

# 4.1 Architecture Design

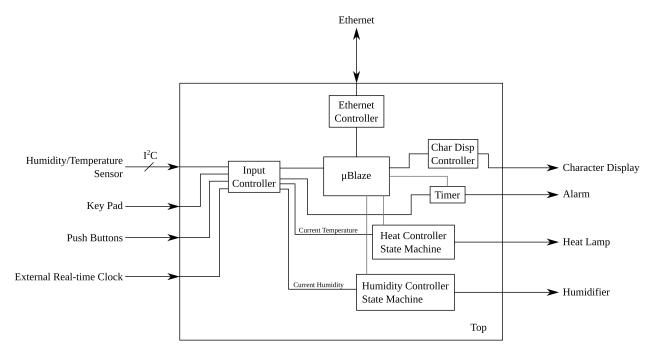

The architecture contains several key components that are directly related to the methods described above. A high-level block diagram of the system can be found in Figure 2. The main purpose of this project is to control a system based on a pre-configured, programmed schedule of environmental conditions and on sensors that monitor the system. The output are signals that manipulate the system by turning on and off power to a heat lamp and humidifier. In order to streamline the creation of the control logic, a MicroBlaze soft-core processor makes up the central core of the architecture. This soft-core processor is in charge of more advanced input processing as well as communication via ethernet to the web server. The set points will be based on the user's programmed input and the current time. A state machine outside of this soft-core processor is be used to make decisions based on the current humidity and temperature and the set-points programmed by the user, then drives the output devices to reach the desired humidity and temperature. The state machine's set-points are updated via a queue controller which keeps track of the current time and status of the proofing box.

Figure 2: Finalized high level block diagram

#### 4.1.1 Changes from Proposal

Most major changes to the project revolved around the use of the MicroBlaze soft-core processor. In the beginning design stages there was some uncertainty about the viability of creating a successful design based on MicroBlaze due to its apparent complexity. Therefore, much of the work was anticipated to be done via IP blocks outside of the processor, meaning only the control logic would be run on MicroBlaze. The block diagram for this initial architectural design can be seen in Figure 3. However, after the team gained a better understanding of the fundamental workings of the MicroBlaze architecture and encountering some difficulty in acquiring IP cores through OpenCores for both Ethernet and I<sup>2</sup>C modules, more tasks were offloaded back onto the soft-core processor.

Figure 3: Initial high level block diagram

In particular, utilizing MicroBlaze made available the AXI IIC IP for I<sup>2</sup>C communication and the AXI Ethernet Lite IP for basic Ethernet communications along with simple usage examples. To allow for more custom VHDL logic to be written and implemented on the FPGA, the control and decision state machines were migrated away from the soft-core processor. This resulted in a more balanced design that takes into consideration both logic level design flow as well as higher level architectural considerations.

# 4.2 Behavior Design

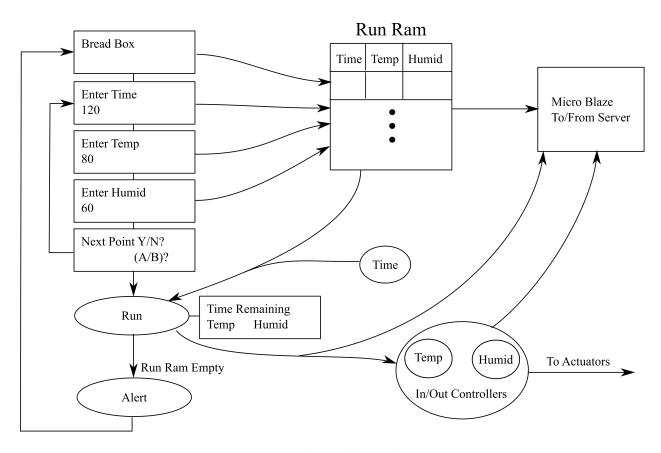

The high level block diagram shows the major components of the design and from it, the RTL modules can be inferred. However, it does not show how the system will behave or how the different components will work together as a whole. In order to design the behavior of the bread box, a high level logic diagram was created and is shown as Figure 4. When the bread box is first powered on the text "Bread Box" will appear on the screen. When

Figure 4: High level logic diagram

any button is pressed the user will be prompted to enter a time for the the stage. Hitting a number key will cause the number to be entered into the system and displayed on the character display. If the wrong number is pressed the 'B' key, or backspace, can be used to remove it one digit at a time. Once a time is entered and the user presses the 'A' key, the user will be prompted to enter the target temperature for the stage. The unit of temperature is degrees Fahrenheit. After the temperature is entered and 'A' is pressed, the user will be prompted to enter the target humidity for the run. Humidity is entered as percent humidity. Once the humidity value is entered and 'A' is pressed, the user will be prompted for the next point. If the user presses 'A' they will be sent back to the enter time page and will be prompted to enter data for the next stage in the run. Each proofing run is built up from multiple smaller stages. Each stage has its own duration and set-points. As the user enters the stages of the run, the points will be stored into the run RAM.

If the user presses 'B' then the first stage of the run will start. The display will show the current state number, the time remaining, the current temperature, and the current humidity. The data for the current stage will be read in from the run RAM. The information about the current run will be sent to the input/output controllers, which will read the current values from the sensors and control the heat lamp and humidifier, so that the set-points for the current stage are reached.

The output control module utilizes a counter that ranges from 0 to 50 for both humidity and temperature to give historical weight to the decision process. For example, if the temperature readings from the sensor have recently been lower than the temperature set point, the weighted counter is closer to 50. Assuming the temperature continues to be lower than the set point, the counter will continue to increment to up until its max weight of 50. Now, if the temperature suddenly shifts to be higher than the set point, the counter reverses its count, slowly shifting its weight towards 0. Once the counter shifts past the threshold of 25 in either direction the corresponding output is toggled. To ensure that this toggling does not occur too quickly and thus degrade or destroy the humidifier and heat lamp components over time, a slow clock is used to update the counters and an even slower clock is used to update the outputs based on these counters.

When the time remaining for the current stage reaches zero the stage will be read in and started. If there are no more stages in the run RAM, the display will show alert and a buzzer will sound. The buzzer will keep sounding until any button is pressed. Once a button is pressed the bread box will return to its initial state and display "Bread Box" once again.

# 5 Division of Labor

It was important that the work laid out in this document could be divided into easily divided parts. Each of these parts had to be discrete enough to allow members of the team to work on their parts independently, without having to wait on unmet dependencies from another team member. The major components of the design are fairly independent from one another. For example, the state machines that control the temperature and humidity could be written without knowing the specifics of how the sensor data is read in. Likewise the sensor interface could be written independently of the other components. The divisions of labor correspond to each of the major aspects of the project: reading and processing

sensor input, processing and tracking user run programming, developing state machines for decision making and output control, assembling the physical components, and designing and interfacing with the web application. By assigning a single group member to predominantly reside over one or more aspects of the design, each design aspect can be accounted for and properly verified. However, throughout the design some of these areas required more work than the others, so each major part was further broken down into minor components and frequently re-assigned to balance the workload between group members.

# 6 Design Flow and Verification Strategy

The design flow of this project closely followed the design flow as laid out in class. This document describes the initial idea and describes the process used to develop the architecture. It also includes a behavioral concept of this design and the results of building a RTL design in which the signal interactions of each component are be mapped and better understood. This involved further development of the behavioral code that describes the functionality of the design. The RTL code can be synthesized into a netlist and placed onto the FPGA for manual testing. All throughout the design, each stage was simulated and verified before the next step in the design proceeded.

The ideal approach to simulating and verifying the functionality of this design would be to break the design into submodules and testing each submodule individually throughout every stage of the design. The most vital submodules are the output control module, the proofing state module, both of which fit into the larger bread proofing top module. By creating test benches for each submodule we can verify that expected outputs are properly generated from the various combinations of inputs. Furthermore, because this project has many other submodules besides these, it becomes necessary to combine the testing of some of these submodules to save time. This combination is achieved by developing a single, higher level test bench for testing various submodules of the design at once. For example, a single test bench can be created for testing the functionality of the I<sup>2</sup>C controller submodule in relation to the temperature and humidity output controller submodule. By combining modules in this way, the tests can verify that not only do the modules achieve their individual intended functionality, but also effectively function across the system in harmony with one other. Once it is verified that multiple combinations of submodules function as intended, even higher level test benches that encompass more modules can be written and run to ensure the entire system of modules works cohesively.

This test bench model did not fit well when developing the web interface. Instead, a more traditional software engineering test structure was used in which a variety of test cases and edge cases were created to exercise and debug the web application to a reasonable standard of operation. This approach may be viewed as analogous to verifying fireproofing via flamethrower rather than by match, as it is much more difficult to control all of the variables in a live and real-world test environment than in a simulated test bench; however, it was decided constructing a mock server would be in the best interest in progressing the interface's development. By facilitating this server to test potential edge cases by sending dummy data, the integration into the eventual Microblaze server proved seamless.

# 7 Verification and Testing

### 7.1 Proofing State Machine

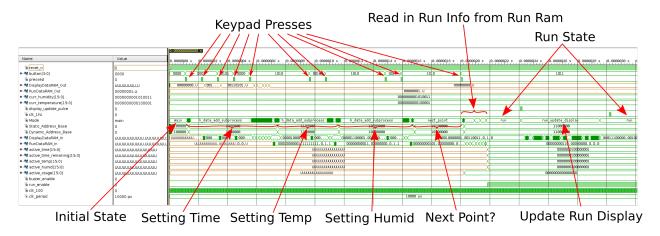

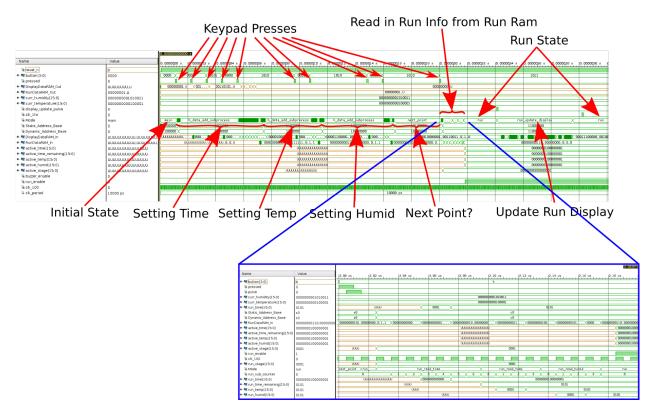

The proofing state machine is one of the main components of the FPGA design. It is in charge of keeping track of the state of the bread box. It also has the important job of reading and writing values to the various memories and providing current run data to all of the other components of the design. Since the proofing state machine is so central to the design, it was verified with the test bench and also incrementally verified using the board. When there were problems with the design, the test bench along with temporary debug values displayed on the LED outputs were used to find the issue.

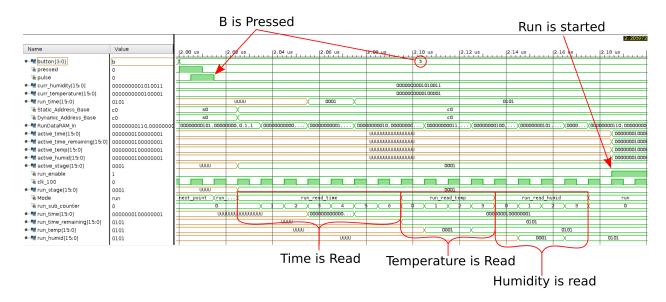

Figure 5: Proofing State Test Bench

Figure 5 shows the test bench used to verify the behavior of the proofing state machine. As the proofing state machine was incrementally built up, the test bench also was incrementally built up to test out the new features of the proofing state machine. The figure shows the final version of the test bench. The test bench was run for the duration of a mock setup run. The transitions of the main state machine and the places where keys were pressed are labeled. This test bench was a great help in verifying that the state machine would function correctly.

Figure 5 shows the waveform for the entire duration of the test bench, because of this, zooming in is necessary to be able to clearly read the state transitions. Let'0s now zoom in on the start of the run to verify this portion of the larger state machine. Figure 6 shows the region from the test bench we will zoom in to focus on. Figure 7 is the zoomed in region.

Figure 7 verifies the start of a bread proofing run once there are no more stages to be entered. At the start of the waveform the Mode is still at next\_point. In this mode the board is waiting for the user to indicate if another stage in the proofing run will be added. The first event that happens is the pressing of the 'B' button by the user. This is shown in the figure by the arrow that points to the pulse signal and the b on the button line. Pulse is used to indicate when a button press should be processed. Pulse will be high for one clock cycle when a button is first pressed. The button press then causes the mode to transition to run\_setup. The run\_setup state is used to initialize the base addresses for

the various RAMs, the run\_sub\_counter, and the run\_stage. Next the mode is changed to run\_read\_time. In this mode, the active run time is read from the run RAM into the local signal run\_time. Since the data is stored as shorts, and the RAM reads a byte at a time, a run\_sub\_counter signal is used to set the signals to correctly read in the value. At the end of the run\_read\_time mode, the run\_time\_remaining is set equal to the run\_time. The next mode is run\_read\_temp, and it reads the current active temperature into the run\_temp signal just like the time was read in. The following mode is run\_read\_humid, and it reads the current active humidity into the run\_humid signal just like the time was read in. The next mode is run. In the run mode, the read in active values are put on the external active\_time, active\_time\_remaining, active\_temp, and active\_humid signals. Additionally, the run\_enable line is set high to indicate that the run has started. Thus we have now verified the correct behavior of this portion of the proofing state machine. The other portions of the state machines were also likewise verified; however, their in-depth verification is not included in this report.

Figure 6: Proofing State Test Bench Zoom Region

Figure 7: Proofing State Test Bench Zoomed and Labeled

# 7.2 Output Control Machine

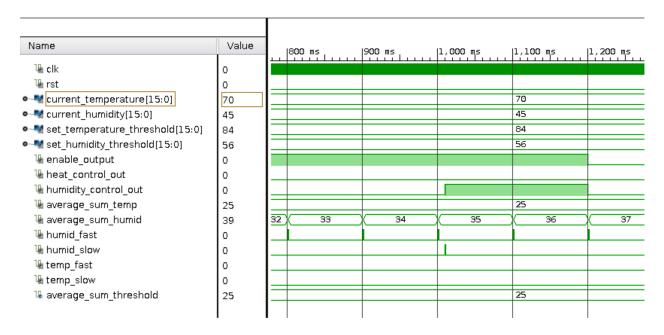

The output control fundamentally operates as a state machine which relies on a set of stored values and a set of values read from the temperature humidity sensor. In order to test the functionality of this state machine, is is necessary to design a test bench that is capable of simulating both preset values and sensor readings on which the state machine will operate. The state machine has predictable outputs based on the inputs provided to it. In reality, this machine is two combined state machines operating independently within the same module. One state machine deals with temperature readings and outputs while the other deals with humidity readings and outputs. The code for these state machines can be found in Appendix A.3. From this code it can be seen that if the set temperature and humidity are higher than the temperature and humidity read from the sensor, then both the humidity and temperature outputs will be high, otherwise they will be low. In the test bench provided in Appendix B.2, the humidity being fed into the control state machine is purposefully set lower than the humidity set point. It is also important to note that the test bench sets the enable\_output signal high in order to signal for the module that it is allowed to change its temperature and humidity outputs. The results can be seen in Figure 8.

Figure 8: Heat lamp and humidifier output control test bench results.

The important signals to watch in this simulation include the ones that affect the humidity output. It can be seen that every pulse from the fast humidity clock brings about an increment in the humidity counter, causing the counter to go above the "on" threshold of decimal value 25. However, the humidity output does not immediately toggle on as soon as this counter reaches 25. This is expected behavior and is done by design to prevent unnecessary strobing of the heat lamp. Therefore, once the slow humidity clock pulses every 15 seconds, the humidity output is finally updated to logic high, meaning the humidifier should now be on, thus increasing the humidity in the box. This particular simulation has successfully verified the anticipated behavior of the VHDL code.

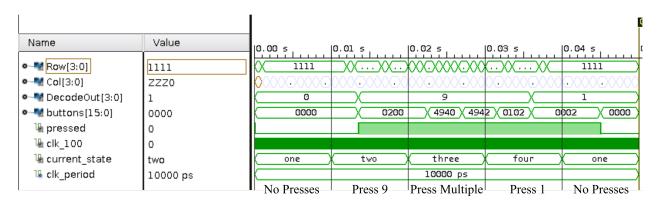

# 7.3 Touch Pad Input

The touch pad input component is used to determine which buttons are pressed on the keypad by scanning the keypad column by column. The component outputs the column to power and reads the rows that have pressed keys. The component outputs the decoded output of a single press, a boolean for when there is a key pressed and the bit masks for the pressed buttons when there is more than one button pressed. When there are multiple buttons pressed the decoded output should hold the value of the last button pressed by itself. The test bench emulates the pressing of no buttons, button "9", multiple buttons simultaneously, button "1", and finally back to no presses. The test bench has asserts throughout it that are used to verify correct behavior. Figure 9 shows the output from running the test bench. From the output one can see that there were no failed asserts in the run.

Note: Testing No presses

Time: 0 ps

Note: Testing press 9

Time: 10 ms

Note: Testing press multiple

Time: 20 ms

Note: Testing press 1

Time: 30 ms

Note: Testing No presses

$Time:\ 40\ ms$

Figure 9: Output from the VHDL test bench asserts.

Figure 10 shows the waveform of the test bench. Current state is the current step being tested. The corresponding tests are labeled below the waveform. The DecodeOut does indeed correspond to the button pressed; it also holds the previous value when multiple buttons are pressed. The buttons bit field correctly updates to the pressed buttons and the pressed boolean also changes correctly.

Figure 10: Keypad Test Bench

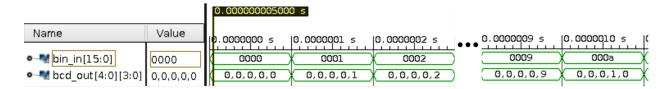

#### 7.4 DoubleDabble

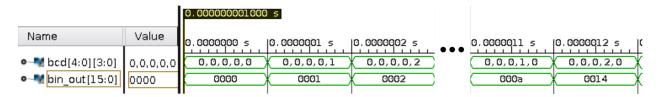

The double dabble component uses the double dabble algorithm to convert binary numbers to binary-coded decimal numbers. The test bench runs through all the possible input values. The waveform shown in figure 11 shows some abbreviated results from the test. The test shows that the binary input is indeed being correctly mapped to a binary-coded decimal.

Figure 11: Double Dabble Test Bench

#### 7.5 BCD 2 Bin

The BCD 2 Bin component does the opposite of the double dabble component. It takes a binary-coded decimal number and converts it into binary. The test bench runs through many of the input combinations. Figure 12 shows the abbreviated results from the test bench. The test shows that the binary-coded decimal number is being correctly converted into a binary number.

Figure 12: BCD 2 Bin Test Bench

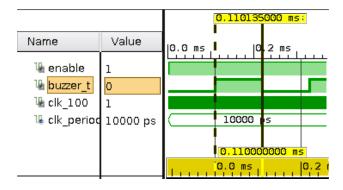

#### 7.6 Buzzer

The buzzer module is in charge of creating a square wave at 20 KHz that will be used to sound the Piezo buzzer. The component has a clock and an enable line for input and generates the 10 KHz wave for output. Figure 13 is used to verify the correct behavior of the module. From the waveform it can be verified that half of the pulse lasts for 0.1 ms which corresponds to a frequency of 20 KHz.

Figure 13: Buzzer Test Bench

#### 7.7 Server-Client Communication

Initially, the primary goal was to set up a server on the FPGA. By utilizing a Microblaze soft processing core, the team was able to modify an echo server for sending a concatenated string containing information related to current temperature, humidity, time remaining, current stage, and stage duration. Because the web interface and Microblaze server communication could not necessarily be test benched using Vivado or ModelSim, other methods of verification had to be utilized. On the client-side, to ensure no time gaps in data, the server is polled every second. This translates into the application sending an acknowledgment to the server indicating that it is ready to receive current readings. On the client-side, output

is displayed indicating successful connection to server and corresponding data retrieval. As aforementioned, the application polls the server every second, and retrieves a concatenated string of temperature, humidity, stage, time remaining, and stage duration values. Figure 14 below details typical connection verification and data retrieval.

```

127.0.0.1 - - [26/Nov/2016 14:36:23] "GET /active/data? =1480188768608 HTTP/1.1" 200 -

Initializing connection to server..

Connection established..

1-second data polling frequency

['81', '59', '1', '37',

127.0.0.1 - - [26/Nov/2016 14:36:24]

"GET /active/data?_=1480188768609 HTTP/1.1" 200 -

Initializing connection to server..

Connection established.

['81', '59', '1', '36',

[Temperature, Humidity, Stage, Time Remaining, Stage Duration]

127.0.0.1 - - [26/Nov/2016 14:36:25]

"GET /active/data?_=1480188768610 HTTP/1.1" 200 -

Initializing connection to server..

Successful communication established with server.

Connection established..

['81', '59', '1', '36',

```

Figure 14: Typical client-side output.

On the server side, upon receiving an acknowledgment from the client that it is prepared to receive measurements, the temperature/humidity is read. Alongside gathering sensor readings, the server also accesses the Run RAM and retrieves information related to current stage, time remaining in corresponding stage, and the duration of the run. After all of the requested data is collected, they are concatenated into a single string and sent to the interface. To ensure the data is properly transferred to the application, the string of readings is displayed on-screen to indicate proper communication and transmission are achieved. Figure 15 below details typical polling and data transmission experienced by the Microblaze server. As can be seen from the same figure, the assigned network parameters are displayed. This indicates that the server setup was successful and it is listening for any potential clients. Alongside displaying the network parameters, the second-by-second sending of data to the web application is also displayed to verify valid readings were taken and data transfer was successful on the server end.

```

-lwIP TCP echo server -

TCP packets sent to port 6001 will be echoed back

link speed: 100

Board IP: 192.168.1.10

Netmask: 255.255.255.0

Gateway: 192.168.1.1

TCP echo server started @ port 7

Temp reading: 68

Hum reading: 59

Concatenated reading: 68,59,1,2,3

Temp reading: 68

Hum reading: 59

Concatenated reading: 68,59,1,2,3

Temp reading: 68

Hum reading: 59

Concatenated reading: 68,59,1,2,3

Temp reading: 68

Hum reading: 58

Concatenated reading: 68,58,1,2,3

```

Figure 15: Server-side communication.

# 7.8 System Level Testing

In addition to using test benches to verify the behavior of the bread box, the team also perform high level system tests on the hardware. These high level tests verified the correct behavior of the system and led to useful discoveries.

The first discovery was that bounds were needed on the numbering so that users could not add numbers past what the screen could show and also so that the users can erase more than the beginning of the screen. These bounds were subsequently put into place and now the users can only enter a max of 5 digits for the numbers and they can also no longer backspace past the beginning of the number.

A second discovery was that a run cancel button would be very useful for the run page. If the user wants to cancel a run gracefully without resetting the board, they can now press the 'E' key to cancel the run and go back to the initial page.

# 8 Results

The final product of the careful design plans that were laid out and executed throughout this project is a fully realized and operational bread proofing box. Although some issues were encountered, these problems were either anticipated or overcome with enough effort. While only a prototype, the design successfully meets and exceeds the goals initially set out in the proposal, and even achieved some stretch goals.

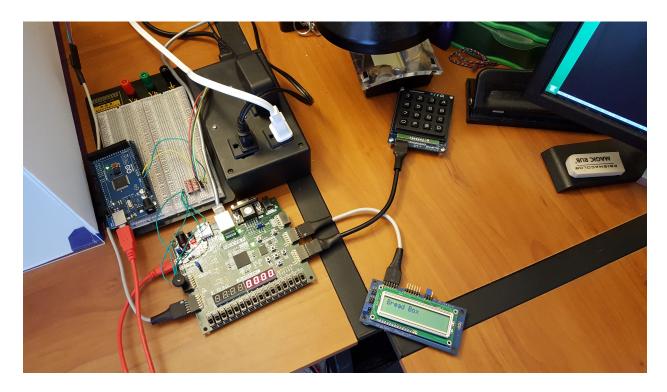

### 8.1 Bread Proofing Box

Figure 16: Bread Proofing Box

The constructed bread-proofing box can be viewed in Figure 16 above. The walls, base, and top of the box were constructed with foam boards and adhered together with duct tape. The front of the box utilized a plastic, transparent sheet for viewing the state of the bread. To the left side of the box is the humidifier. By severing a hole into the side of the box, the humidifier was successfully attached via drier duct. By strategically cutting an opening atop the box, the heat lamp is able to securely rest directly over the bread. Inside the enclosure, near the back-right corner, is where the temperature/humidity sensor resides. The team tactically positioned it to be mid-height, away from direct light to achieve balanced humidity and temperature readings.

In the Figure 17 below, the electronics for the bread proofing box can be seen. To the top-right is the functional keypad for entering in set time, set temperature, and set humidity. To the bottom-right is the character display for displaying information related to the current stage, current temperature, current humidity, and time remaining in the stage. To the left of the character display, is the Nexys 4 board itself. Connected to the Nexys 4 board is a piezo buzzer and wires leading to a switch box just above the FPGA. The Arduino board on the left-side is exclusively used to provide 5V power to the relays in the switch box that control the humidifier and heat lamp. Finally, the gray-wired pin connector at the bottom-left extends to connect to the temperature/humidity sensor situated within the box.

Figure 17: View of bread box electronics

#### 8.2 Controls

The bread proofing box worked correctly according to the behavior design outlined in Section 4.2. The following pictures show the control of the bread box with the keypad and character display. Figure 18 shows the initial page and welcome screen. Figure 19 shows the page used to set the duration of a stage. 120 minutes have been entered for the duration. Figure 20 shows the page used to set the temperature set point for the stage. 80 Degrees has been entered as the target temperature. Figure 21 shows the page used to set the humidity set point. 70% humidity has been entered. Figure 22 shows the next point page. 'A' is pressed for yes and 'B' is pressed for no. Figure 23 shows the page that displays information regarding the current stage while the bread box is running. 'S' stands for state and shows the number of the current state. This number starts at 1 and increases for each additional point in the run. 'R' stands for remaining and shows the time remaining in the current stage. 'T' stands for temperature and shows the current temperature in the box. 'H' stands for humidity and shows the current humidity in the box.

Figure 18: Initial Page

Figure 19: Time Page

Figure 20: Temperature Page

Figure 21: Humidity Page

Figure 22: Next Point Page

Figure 23: Run Page Page

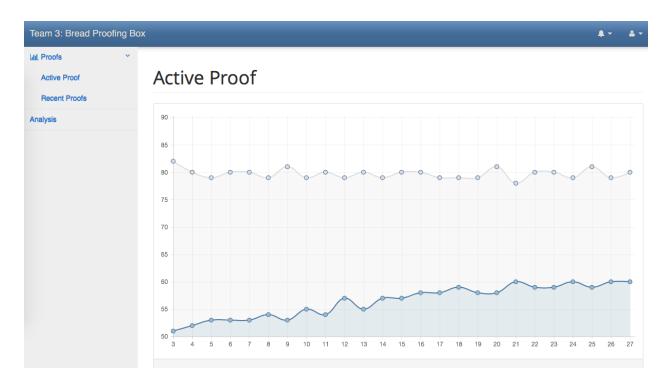

#### 8.3 Web Interface

As detailed previously, the web interface acts as a client that frequently polls the Microblaze for temperature, humidity, and timing information. By parsing through the received data, the values are then displayed graphically on a minute-by-minute basis for the first thirty minutes. As time progresses, the resolution of graphical display decreases, as depicted in the Table 2 below. This is due to the specific chart package for the interface. Without the premium package, the values would get truncated to the point of unreadability; therefore, specific set-points are dynamically selected for displaying based upon the number of data points themselves.

| Datapoints | Resolution   |

|------------|--------------|

| 30         | 1-min        |

| 60         | 2-min        |

| 90         | 3-min        |

| 120        | 4-min        |

| 150        | 5-min        |

| 180        | 6-min        |

| 210        | $7$ - $\min$ |

| 240        | 8-min        |

| 270        | 9-min        |

| 300        | 10-min       |

| 330        | 11-min       |

| 360        | 12-min       |

Table 2: Data resolutions for graphical analysis.

Figure 24: Home screen of interface at minute 3 of an ongoing stage.

Figure 25: Active proof at minute 27 of an ongoing stage.

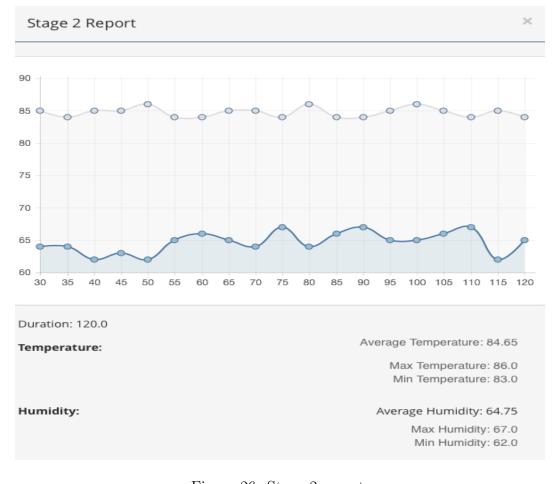

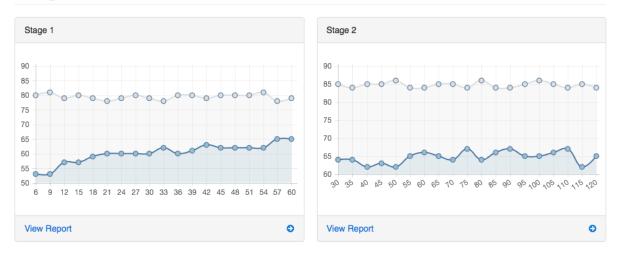

Alongside the displaying of temperature and humidity values, the team felt that saving previous stage data would also be necessary. To accomplish this predefined stretch goal, a MySQL server was facilitated. By allowing the web framework to gain access to the MySQL server, the first three stages are capable of being stored. The manner in which the stages are saved are determined by the stage value provided by the Microblaze server. Specifically, by storing each current stage value as a session variable, the application compares the new stage value to the old one. If the new stage value is "0" (indicating that the entire bread proofing run has finalized) or greater than the previous stage value, the application knows to store the previous stage data. This requires deleting any previous runs, resetting the previous stage's temperature, humidity, and time lists, and incrementing the stage counter. Figures 26 and 27 detail two saved runs available for users to view. As shown in the images, by clicking on a saved stage, a user can view the duration, min/max, and average values experienced throughout the stage.

Figure 26: Stage 2 report.

# **Stages**

Figure 27: Saved stages available for viewing.

### 8.4 Bread Making

Once the bread box became functional, it was time to make bread. The actual steps to making the bread is a product of experience and no longer follows a fixed recipe; however, the recipe that was used when starting out is included in Appendix D. The main steps to bread making are mixing, autolyse, first knead, bulk ferment and folding, second knead, shaping, final proof, scoring, and baking. Different bakers follow different methods and bread making is sill very much an art form. The essential ingredients are water, flour, and salt. Starter is also needed but can be cultivated by leaving a mixture of water and flour sitting out. The starter our team used originally came from King Arthur Flour and has since been kept going for 3 years. In addition to the necessary ingredients, sugar and olive oil were also added. The sugar and the olive oil provide additional flavor. Additionally, the olive oil helps to soften the crust, but can also lead to smaller air pockets.

The following figures are all from the various steps of making bread. The pictures are from two separate uses of the bread box. Figures 28 and 29 are a before and after for the bulk fermenting step for the first use. The resulting bread is shown in Figure 30. Figures 31 and 32 show the interior porous crumb of the bread.

Figure 33 shows the second run bread after the final proof step. The finished bread is shown in Figure 34. The crumb is shown in Figure 35.

During the first run, the dough was not folded during the bulk fermentation stage. Not folding the bread allowed time lapse footage to be made and allowed for an impressive before and after picture. During the second run, the dough was folded during the bulk fermentation stage. This caused the glutton structure to form better, which caused the loaf to rise better in the oven. This change is the main reason the bread from the second run is taller and airier than the first run.

Figure 28: Before bulk ferment.

Figure 29: After bulk ferment.

Figure 30: Bread produced from first use.

Figure 31: Crumb of first artisan loaf.

Figure 32: Crumb of first sandwich loaf.

Figure 33: Final Proof of second bread.

Figure 34: Bread produced from second use.

Figure 35: Crumb of second artisan loaf.

# 9 Future Work

### 9.1 Improvements

Although the project successfully met all the goals laid out for it, the team did uncover various areas of future work while implementing the bread proofing box.

#### 9.1.1 Enclosure

While testing the bread proofing box, the team discovered that the humidity will naturally rise when moist dough is placed in a warm enclosure. Unfortunately, it is unknown if the increase in moisture was caused by water evaporating from the surface of the bread or if it was evaporating from the water reservoir of the humidifier. Since the humidity of the enclosure rose past the set point without the humidifiers input, future work would be to determine the source of the increased humidity and to determine is a humidity removal system is needed.

The team also discovered that the light is not all that great at holding a steady temperature reading by the sensors. With a max toggle rate of 15 seconds, the temperature is able to fluctuate by about  $\pm 2$  degrees. This issue could be resolved by using a dimmer switch to control the light. The dimmer switch would allow the light to be dimmed to hold the temperature at a steady level.

Another observation was that the foam board is not water proof, which could potentially cause problems with the longevity of the box, especially since running at high humidity levels can cause condensation to form bubbles on the walls. The box also began to warp after only 3 days of use. This could be a result of moisture inside the box affecting the walls or from the weight of the lid itself. Moister is the most likely cause since the acrylic, with the back wall edges, should be able to hold the lid without problems. The side walls would need some sort of reinforcement to increase durability. Figure 36 shows the gap that has formed between the acrylic and the side wall. When the box was first built, the acrylic was flush against the outer wall.

Figure 36: Walls are starting to warp outward.

#### 9.1.2 Web Interface

In the saving and viewing previous stages within a run, the team encountered several challenges. These challenges pertained to the linking of the MySQL server. Occasionally, upon deleting and saving new runs, the database would lock up and freeze upon executing queries. The remedy to this was simply restarting the MySQL server, and initializing the run again. However, for stages lasting hours with a vast array of data, it would be tremendously inconvenient for the data to not save properly due to database server lock-ups. Therefore, a new approach to database linking is recommended. For instance, because the interface and server has internet access, utilizing more consistent database options such as Google Firebase could prove advantageous. However, drawbacks may correspond to always requiring internet access to save proofing runs and potential network security concerns.

#### 9.2 Additional Features

#### 9.2.1 Enclosure

Additional future work also includes adding new features to the bread box. One such feature is the addition of the real-time clock module to allow the timer to be more accurate. Although using a counter for the on-board 100 MHz clock seems to allow the timer to keep accurate time, a more accurate external real-time clock could improve the timers accuracy for long runs. It could also enable the creation of additional features, like delayed start and ending at a given clock time. Another feature possibility, would be the addition of sensors to monitor the bread as it rises. One possible sensor for this end is an ultrasonic sensor to measure the height of the bread.

#### 9.2.2 Web Interface

For expanding the capabilities of the web interface, the database can be linked within the Microblaze server itself. Ideally, this would be the preferred approach as the data would be stored on the server-side as opposed to the client-side. Due to time constraints and the lack of hardware availability (single FPGA board for the entire group), this approach was unattainable. Currently, the interface is only capable of displaying data once it connects to the server, which could potentially disregard many previous data points; however, by accessing the database on the server-side, the run data will be available, from their initial stages, for display across all prospective clients.

# 10 Conclusion

Sourdough bread making is age-old process that is as much as an art form as it is science in action. Experience and scientific knowledge is needed to make great bread. With the help of modern technology, the kitchen can become a scientific playground and a laboratory of art, allowing great discoveries to come about from chance and controlled experiments. This project set out to design and build a custom bread proofing box that utilizes the skills of modern engineers and takes advantage of the modern technological capabilities found on the Nexys 4 board. By documenting and following a well-defined design specification, the project found greater success in not only laying out realistic goals, but also in reaching and surpassing those goals. As a result, a fully-functioning bread proofing box was created. By allowing users the capability of monitoring their bread in a controlled environment, they are able to establish optimal proofing conditions to further enhance and progress the art of bread making.

# Appendix A VHDL Source Code

### A.1 Bread Box Top-level

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use work.common.all;

entity top is

port (

- General Ports

clk_100

: in std_logic; — 100 MHz clock

: in std_logic; -- reset signal

reset_n

: in std_logic_vector(15 downto 0); — Switches for Debug

sw

: out std_logic_vector(15 downto 0); — LED for debug

led

RGB1\_Red

: out std_logic;

: out std_logic;

RGB2_Blue

: out std_logic_vector(7 downto 0); -- Seg for debug

seg

: out std_logic_vector(7 downto 0); -- Seq for debug

an

-- Character Display

JA: inout STD_LOGIC_VECTOR (7 downto 0);

-- Keypad

JB : inout std_logic_vector (7 downto 0);

— RTC & Humidity and Temperature Sensor

JC : inout std_logic_vector(7 downto 0);

JD : inout std_logic_vector(7 downto 0);

- USB Uart for debug messages from micro blaze

usb_uart_rxd : in std_logic;

usb_uart_txd : out std_logic;

-- Ethernet

PhyClk50Mhz : out std_logic;

PhyMdc

: out STD_LOGIC;

PhvCrs

: in STD_LOGIC;

PhyRxErr

: in STD_LOGIC;

PhyRxd

: in STD_LOGIC_VECTOR ( 1 downto 0 );

PhyTxEn

: out STD_LOGIC;

PhyTxd

: out STD_LOGIC_VECTOR ( 1 downto 0 );

PhyMdio

: inout STDLOGIC;

- Cellular memory

MemAdr

: out STD_LOGIC_VECTOR ( 22 downto 0 );

RamADVn

: out STD_LOGIC;

RamLBn

: out std_logic;

: out std_logic;

RamUBn

RamCEn

: out STD_LOGIC;

RamCRE

: out STD_LOGIC;

: out STD_LOGIC;

RamOEn

RamWait

: in STDLOGIC;

```

```

RamWEn

: out STD_LOGIC;

MemDB

: inout STDLOGIC_VECTOR ( 15 downto 0 )

end entity top;

architecture structural of top is

-- Components

- Micro Blaze

component processing_core_wrapper

ETH_mdio_mdc_mdc : out STD_LOGIC;

ETH_rmii_crs_dv : in STD_LOGIC;

ETH_rmii_rx_er : in STD_LOGIC;

ETH_rmii_rxd : in STD_LOGIC_VECTOR ( 1 downto 0 );

ETH_rmii_tx_en : out STD_LOGIC;

ETH_rmii_txd : out STD_LOGIC_VECTOR ( 1 downto 0 );

USB_Uart_rxd : in STD_LOGIC;

USB_Uart_txd : out STD_LOGIC;

cellular_RAM_addr : out STD_LOGIC_VECTOR ( 22 downto 0 );

cellular_RAM_adv_ldn : out STD_LOGIC;

cellular_RAM_ben : out STDLOGIC_VECTOR ( 1 downto 0 );

cellular_RAM_ce_n : out STD_LOGIC;

cellular_RAM_cre : out STD_LOGIC;

cellular_RAM_oen : out STD_LOGIC;

cellular_RAM_wait : in STD_LOGIC:

cellular_RAM_wen : out STD_LOGIC;

cellular_ram_dq_io : inout STD_LOGIC_VECTOR ( 15 downto 0 );

curr_humid_tri_o : out STD_LOGIC_VECTOR ( 15 downto 0 );

curr_temperature_tri_o : out STD_LOGIC_VECTOR ( 15 downto 0 );

duration_tri_i : in STDLOGIC_VECTOR ( 15 downto 0 );

eth_mdio_mdc_mdio_io : inout STD_LOGIC;

eth_ref_clk : out STD_LOGIC;

gpio_stage_tri_i : in STDLOGIC_VECTOR ( 15 downto 0 );

iic_rtl_scl_io : inout STD_LOGIC;

iic_rtl_sda_io : inout STD_LOGIC;

remaining_tri_i : in STD_LOGIC_VECTOR ( 15 downto 0 );

reset : in STD_LOGIC;

sys_clock : in STD_LOGIC

);

end component;

-- Counter to generate SCL

component c_counter_binary_0 IS

PORT (

CLK: IN STD_LOGIC;

Q : OUT STDLOGIC_VECTOR(11 DOWNIO 0)

);

END component;

-- Seven segment display controller

component display

```

```

: in STD_LOGIC_VECTOR (15 downto 0);

Port ( data

: in STD_LOGIC;

carry

: in STD_LOGIC;

seg_number : out STD_LOGIC_VECTOR (63 downto 0) );

end component;

-- Seven segment component

component sSegDisplay

Port (ck

: in

std_logic;

-- 100MHz system

clock

reset_n : in std_logic;

- Reset signal

number: in std_logic_vector (63 downto 0); — eight digit

number to be displayed

: out std_logic_vector (7 downto 0); — display

seg

cathodes

: out std_logic_vector (7 downto 0)); -- display anodes

(active-low, due to transistor complementing)

end component;

component RAM_2K_8

port (

DOA: out std_logic_vector(7 downto 0);

DOB : out std_logic_vector(7 downto 0);

DOPA : out std_logic_vector(0 downto 0);

DOPB : out std_logic_vector(0 downto 0);

ADDRA: in std_logic_vector(10 downto 0);

ADDRB: in std_logic_vector(10 downto 0);

CLKA: in std_logic;

CLKB : in std_logic;

DIA: in std_logic_vector(7 downto 0);

DIB : in std_logic_vector(7 downto 0);

DIPA : in std_logic_vector(0 downto 0);

DIPB : in std_logic_vector(0 downto 0);

ENA : in std_logic;

ENB : in std_logic;

SSRA : in std_logic;

SSRB : in std_logic;

WEA : in std_logic;

WEB: in std_logic

);

end component;

component Constant_Character_RAM

port (

DOA: out std_logic_vector(7 downto 0);

DOB: out std_logic_vector(7 downto 0);

DOPA : out std_logic_vector(0 downto 0);

DOPB : out std_logic_vector(0 downto 0);

ADDRA: in std_logic_vector(10 downto 0);

ADDRB: in std_logic_vector(10 downto 0);

CLKA : in std_logic;

CLKB : in std_logic;

DIA : in std_logic_vector(7 downto 0);

DIB : in std_logic_vector(7 downto 0);

```

```

DIPA : in std_logic_vector(0 downto 0);

DIPB : in std_logic_vector(0 downto 0);

ENA : in std_logic;

ENB : in std_logic;

SSRA : in std_logic;

SSRB : in std_logic;

WEA : in std_logic;

WEB : in std_logic

);

end component;

component Message_Setter

Port (

CLK: in STD_LOGIC;

-- Clock

-- Pulse to update

Update_Pulse : in std_logic;

the screen

Reset: in STDLOGIC;

-- Reset

Static_Address_Base: in integer range 0 to 2047; — Base address for

static display

Dynamic_Address_Base: in integer range 0 to 2047; — Base address for

dynamic display

ProcDataRAM_In : out T_RAM_Port_In :

-- Processed Data

Ram

ProcDataRAM_Out : in T_RAM_Port_Out;

-- Processed Data

Ram

ConstCharRAM_In : out T_RAM_Port_In;

-- Constant Char RAM

ConstCharRAM_Out : in T_RAM_Port_Out;

-- Constant Char RAM

DispCLR: out STDLOGIC;

- Clear Display

DispClearMem : out STD_LOGIC;

- Clear Display Mem

DispAddr: out integer range 0 to 31;

— Display Mem Addr

DispData: out STD_LOGIC_VECTOR (7 downto 0);

-- Display Data

DispDataEnable : out STD_LOGIC;

-- Display Data

Enable

UpdateDisplay : out STDLOGIC;

- Update Char

Display

- Display Updating

DispInProg : in STDLOGIC);

end component;

component CharDisplay

Port ( CLK : in STD_LOGIC;

--clock

-- Reset

Reset: in STDLOGIC;

CLR: in STD_LOGIC;

--clears screen

only

ClearMem: in STD_LOGIC:

-- clears memory

RST: in STD_LOGIC;

--- sets screen to

power up state - clears screen

DAddr: in integer range 0 to 31;

--address of new

character

DataIn : in STD_LOGIC_VECTOR (7 downto 0);

-- New character

DataInEnable : in STD_LOGIC;

--signal to read

in new character

```

```

UpdateDisplay : in STDLOGIC;

DispInProg : out STDLOGIC;

-- Indicates new

line display

JA: inout STDLOGIC-VECTOR (3 downto 0)); —pins of CLS

Display

end component;

component Keypad

Port (

clk

: in std_logic;

: in std_logic_vector (3 downto 0);

Row

: out std_logic_vector (3 downto 0);

Col

-- Last number pressed by itself

DecodeOut : out std_logic_vector (3 downto 0);

- Vector of the buttons pressed

: out std_logic_vector (15 downto 0);

-- Boolean if buttons are pressed.

pressed : out std_logic

);

end component;

-- RTC

component RTC is

port (

clk : in std_logic;

rst : in std_logic;

SCL : inout std_logic;

SDA: inout std_logic

end component;

component output_control is

Port (

clk : in STD_LOGIC;

rst : in std_logic;

curr_temperature : in STD_LOGIC_VECTOR (15 downto 0);

curr_humidity : in STD_LOGIC_VECTOR (15 downto 0);

set_temperature : in std_logic_vector(15 downto 0);

set_humidity : in std_logic_vector(15 downto 0);

enable : in std_logic;

heat_control : out STDLOGIC;

humid_control : out STD_LOGIC

end component;

component Proofing_State

Port (

CLK.

-- System

clock

- Reset

reset_n : in std_logic;

display_update_pulse : in std_logic;

- pulse to

update run display

clk_1hz : in std_logic;

-- One hertz

clock used to update the timer

```

```

button: in std_logic_vector (3 downto 0);

press from keypad

-- Pressed

pressed : in std_logic;

from keypad

curr_humidity : in std_logic_vector(15 downto 0);

-- Current

humidity from the sensor

curr_temperature: in std_logic_vector(15 downto 0); -- Current

temperature from the sensor

-- Current

Mode : out t_proofer_state;

mode of the state machine

Static_Address_Base : out integer range 0 to 2047;

address for static display

Dynamic_Address_Base : out integer range 0 to 2047; — Base

address for dynamic display

DisplayDataRAM_In : out T_RAM_Port_In;

-- Display

Data Ram

DisplayDataRAM_Out : in T_RAM_Port_Out;

-- Display

Data Ram

RunDataRAM_In : out T_RAM_Port_In;

-- Run Data

Ram

RunDataRAM_Out : in T_RAM_Port_Out;

-- Run Data

Ram

buzzer_enable : out std_logic;

-- Enable the

buzzer

active_time : out std_logic_vector(15 downto 0); — Active Time

active_time_remaining : out std_logic_vector(15 downto 0); --

Remaining time for the run

active_temp : out std_logic_vector(15 downto 0);

-- Active

Temperature

active_humid : out std_logic_vector(15 downto 0); — Active

Humidity

active_stage : out std_logic_vector(15 downto 0);

stage

-- Is the

run_enable : out std_logic

device running?

);

end component;

component CDiv

TC: integer := 18 -- Time Constant. 15 for ^{\circ}1khz -- 500000000/(

TC^4) Hz

);

PORT (

Cin

: IN STD_LOGIC;

Reset: IN STD_LOGIC;

Cout : OUT STD_LOGIC);

end component;

component buzzer

port (

clk_100 : in std_logic;

enable : in std_logic;

buzzer : out std_logic

```

-- Button

```

end component;

-- Signals

signal reset

: std_logic;

: std_logic;

signal clk

- Signals for output display

signal result_data : std_logic_vector(15 downto 0);

signal carry : std_logic;

signal display_number : std_logic_vector (63 downto 0);

-- Microblaze

signal cellular_RAM_ben : std_logic_vector(1 downto 0);

-- Bread Machine Control

signal current_state : t_proofer_state;

signal real_time_clk : std_logic;

signal update_run_display : std_logic;

- Output control signals

signal buzzer_enable : std_logic;

-- Character display signals

signal Static_Address_Base : integer range 0 to 2047; — Base address for

static display

signal Dynamic_Address_Base: integer range 0 to 2047; — Base address for

dynamic display

-- Keypad

signal keypad_pressed : std_logic;

signal keypad_button : std_logic_vector(3 downto 0);

- Parser to Ram

signal parser_to_RAM_In : t_RAM_Port_In;

signal parser_to_RAM_Out : t_RAM_Port_Out;

-- Processed Ram to Message Setter

signal Proc_to_Msg_Setter_In : t_RAM_Port_In;

```

```

signal Proc_to_Msg_Setter_Out : t_RAM_Port_Out;

-- Const Ram to Message Setter

signal const_to_Msg_Setter_In : t_RAM_Port_In;

signal const_to_Msg_Setter_Out : t_RAM_Port_Out;

- Data Ram to Calculation Block

signal Data_RAM_in: t_RAM_Port_In;

signal Data_RAM_out: t_RAM_Port_Out;

-- Calculation Block to Processed Ram

signal Proc_RAM_in: t_RAM_Port_In;

signal Proc_RAM_out: t_RAM_Port_Out;

-- Slow update pulse for Message Setter

signal update_char : std_logic;

-- Char Display

type t_char_disp is record

DispCLR : std_logic;

DispClearMem : std_logic;

DispAddr: integer range 0 to 31;

DispData : STDLOGIC_VECTOR (7 downto 0);

DispDataEnable : std_logic;

UpdateDisplay : std_logic;

DispInProg : std_logic;

end record;

signal char_disp : t_char_disp;

-- I2C Signals

signal q : std_logic_vector(11 downto 0);

signal err : std_logic;

signal Dout : std_logic_vector(7 downto 0);

signal \ clk_i 2c : std_logic := '0';

-- Live data signals

signal curr_humidity : std_logic_vector(15 downto 0);

signal curr_temperature : std_logic_vector(15 downto 0);

-- Set data signals

signal set_temperature : std_logic_vector(15 downto 0);

signal set_humidity : std_logic_vector(15 downto 0);

signal enable_output : std_logic;

-- Time Signals

signal curr_duration : std_logic_vector(15 downto 0);

```

```

signal curr_remaining: std_logic_vector(15 downto 0);

signal active_stage : std_logic_vector(15 downto 0);

- Output control

signal humidity_out

: std_logic;

signal temperature_out : std_logic;

begin

-- Set the reset

reset <= not reset_n;

display_logic : display

port map (

data

=> result_data,

carry

\Rightarrow carry,

\Rightarrow clk_100,

seg_number => display_number

);

carry <= '0';

seven_seg_driver : sSegDisplay

port map (

ck

\Rightarrow clk_100,

reset_n

\Rightarrow reset_n,

number

=> display_number,

seg

\Rightarrow \operatorname{seg},

an

\Rightarrow an

);

-- RTC

real\_time\_clock: RTC

port map (

clk \implies clk_{-}i2c,

rst \implies reset,

SCL \implies JC(2),

SDA \implies JC(3)

);

Touch_pad : Keypad

Port map (

clk \Rightarrow clk_100,

Row \Rightarrow JB(7 downto 4),

Col \Rightarrow JB(3 \text{ downto } 0),

DecodeOut => keypad_button,

pressed => keypad_pressed

);

control : output_control

Port map (

clk \Rightarrow clk_100,

rst \Rightarrow reset,

```

```

curr_temperature => curr_temperature,

curr_humidity => curr_humidity ,

set_temperature => set_temperature,

set_humidity => set_humidity,

enable => enable_output,

heat_control => temperature_out,

humid_control => humidity_out

);

JD(6) <= not humidity_out;

JD(7) <= not temperature_out;

c_state : Proofing_State

Port map (

CLK \Rightarrow clk_100,

reset_n => reset_n,

display_update_pulse => update_run_display,

clk_1hz => real_time_clk,

button => keypad_button,

pressed => keypad_pressed ,

curr_humidity => curr_humidity,

curr_temperature => curr_temperature,

Mode => current_state,

Static_Address_Base => Static_Address_Base,

Dynamic_Address_Base => Dynamic_Address_Base,

DisplayDataRAM_In => Proc_RAM_in,

DisplayDataRAM_Out => Proc_RAM_out,

RunDataRAM_In \Rightarrow Data_RAM_in,

RunDataRAM_Out => Data_RAM_out,

buzzer_enable => buzzer_enable,

active_temp => set_temperature,

active_humid => set_humidity,

run_enable => enable_output,

active_time => curr_duration,

active_time_remaining => curr_remaining,

active_stage => active_stage

);

-- Clock divider used to choose when to show new data from the sensors

display_update : CDiv

generic map(

TC \implies 118)

port map(

Cin \implies CLK_100,

Reset \Rightarrow '0',

Cout => update_run_display);

-- Clock divider used to generate a 1 hertz clock

real_time : CDiv

generic map(

TC \implies 100

port map(

Cin \Rightarrow CLK_100,

Reset \Rightarrow '0',

```

```

Cout => real_time_clk);

micro_proc : processing_core_wrapper

port map (

= clk_100,

sys_clock

reset

\Rightarrow reset,

USB_Uart_rxd

=> usb_uart_rxd,

USB\_Uart\_txd

=> usb_uart_txd ,

ETH_mdio_mdc_mdc

\Rightarrow PhyMdc,

ETH_rmii_crs_dv

=> PhyCrs,

ETH_rmii_rx_er

=> PhvRxErr,

ETH_rmii_rxd

\Rightarrow PhyRxd,

ETH_rmii_tx_en

\Rightarrow PhyTxEn,

ETH_rmii_txd

\Rightarrow PhyTxd,

cellular_RAM_addr

\Rightarrow MemAdr,

=> RamADVn,

cellular_RAM_adv_ldn

cellular_RAM_ben

=> cellular_RAM_ben,

cellular_RAM_ce_n

\Rightarrow RamCEn,

cellular_RAM_cre

=> RamCRE,

cellular_RAM_oen

=> RamOEn,

cellular_RAM_wait

\Rightarrow RamWait,

cellular_RAM_wen

=> RamWEn,

=> MemDB.

cellular_ram_dq_io

eth_mdio_mdc_mdio_io

=> PhyMdio,

eth_ref_clk

\Rightarrow PhyClk50Mhz,

iic_rtl_scl_io

\Rightarrow JC(2),

iic_rtl_sda_io

\Rightarrow JC(3),

curr_temperature_tri_o

=> curr_temperature,

curr_humid_tri_o

=> curr_humidity,

duration_tri_i

=> curr_duration,

remaining_tri_i

=> curr_remaining,

gpio_stage_tri_i

=> active_stage

);

RamUBn <= cellular_RAM_ben(1);

RamLBn \le cellular_RAM_ben(0);

-- Run Ram

data_ram : RAM_2K_8

port map (

DOA => parser_to_RAM_Out.DO,

DOB \Rightarrow Data_RAM_out.DO,

DOPA => parser_to_RAM_Out.DOP,

DOPB \Rightarrow Data_RAM_out.DOP,

ADDRA => parser_to_RAM_In.ADDR,

ADDRB \Rightarrow Data_RAM_in.ADDR

CLKA \Rightarrow CLK_100,

CLKB \Rightarrow CLK_100,

DIA => parser_to_RAM_In.DI,

DIB => Data_RAM_in.DI,

DIPA => parser_to_RAM_In.DIP,

DIPB => Data_RAM_in.DIP,

ENA => parser_to_RAM_In.EN,

```

```

ENB \Rightarrow Data_RAM_in.EN

SSRA \Rightarrow Reset,

SSRB \Rightarrow Reset,

WEA => parser_to_RAM_In.WE,

WEB \implies Data_RAM_{in}.WE

);

-- Processed Date Ram

Proc_RAM : RAM_2K_8

port map (

DOA \Rightarrow Proc_RAM_Out.DO,

DOB => Proc_to_Msg_Setter_Out.DO,

DOPA \Rightarrow Proc_RAM_Out.DOP,

DOPB => Proc_to_Msg_Setter_Out.DOP,

ADDRA \Rightarrow Proc_RAM_in.ADDR

ADDRB => Proc_to_Msg_Setter_In .ADDR,

CLKA \Rightarrow CLK_100,

CLKB \Rightarrow CLK_100,

DIA \Rightarrow Proc_RAM_in.DI,

DIB => Proc_to_Msg_Setter_In.DI,

DIPA \Rightarrow Proc_RAM_in.DIP,

DIPB => Proc_to_Msg_Setter_In.DIP,

ENA \Rightarrow Proc_RAM_{in}.EN

ENB \Rightarrow Proc_to_Msg_Setter_In.EN

SSRA \Rightarrow Reset,

SSRB \Rightarrow Reset,

WEA \implies Proc_RAM_in.WE

WEB => Proc_to_Msg_Setter_In.WE

);

-- Constant Date Ram

Const_RAM : Constant_Character_RAM

port map (

DOA => const_to_Msg_Setter_Out.DO,

DOB \Rightarrow open,

DOPA => const_to_Msg_Setter_Out.DOP,

DOPB \Rightarrow open,

ADDRA \implies const_to_Msg_Setter_In .ADDR,

ADDRB \Rightarrow (others \Rightarrow '1'),

CLKA \Rightarrow CLK_100,

CLKB \Rightarrow '1',

DIA \implies const_to_Msg_Setter_In.DI,

DIB \Rightarrow (others \Rightarrow '1'),

DIPA => const_to_Msg_Setter_In.DIP,

DIPB \Rightarrow (others \Rightarrow '1'),

ENA \Rightarrow const_to_Msg_Setter_In.EN,

ENB \Rightarrow '0'

SSRA \Rightarrow Reset,

SSRB \Rightarrow '0',

WEA \Rightarrow const_to_Msg_Setter_In.WE

WEB \Rightarrow '0'

);

-- Message Setter

```

```

msg_setter : Message_Setter

port map (

CLK \Rightarrow CLK_{-}100,

Update_Pulse => update_char,

Reset => Reset,

ProcDataRAM_In => Proc_to_Msg_Setter_In,

ProCDataRAM_Out => Proc_to_Msg_Setter_Out,

ConstCharRAM_In => const_to_Msg_Setter_In ,

ConstCharRAM_Out => const_to_Msg_Setter_Out,

DispCLR => char_disp.DispCLR,

DispClearMem => char_disp.DispClearMem,

DispAddr => char_disp.DispAddr,

DispData => char_disp.DispData,

DispDataEnable => char_disp.DispDataEnable,

UpdateDisplay => char_disp.UpdateDisplay,

DispInProg => char_disp.DispInProg,

Static_Address_Base => Static_Address_Base,

Dynamic_Address_Base => Dynamic_Address_Base

);

-- Communication to the CharDisplay

CDisplay: CharDisplay port map (

CLK \Rightarrow CLK_100,

Reset => Reset,

CLR \Rightarrow char_disp.DispCLR,

ClearMem => char_disp.DispClearMem,

RST \Rightarrow Reset,

DAddr => char_disp.DispAddr.

DataIn => char_disp.DispData,

DataInEnable => char_disp.DispDataEnable,

UpdateDisplay => char_disp.UpdateDisplay,

DispInProg => char_disp.DispInProg,

JA \Rightarrow JA(3 \text{ downto } 0);

-- Clock divider used to get a slow clock for the Seven Segment display

divset : CDiv

generic map(

TC \Rightarrow 35

port map(

Cin \Rightarrow CLK_100,

Reset \Rightarrow '0',

Cout => update_char);

generate_scl : process(q)

begin

if(q = x"1F4") then

clk_i 2c \le not clk_i 2c;

end if;

end process generate_scl;

alert : buzzer

port map (

clk_100 \Rightarrow clk_100,

enable => buzzer_enable,

```

```

\begin{array}{rcl} \text{buzzer} & \Rightarrow \text{JD}(3) \\ ); \end{array}

```

${\bf end\ architecture}\,;$

## A.2 Proofing State Machine

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC.STD.ALL;

use IEEE.STDLOGIC_UNSIGNED.ALL;

library work;

use work.common.all;

entity Proofing_State is

Port (

CLK,

System clock

reset_n : in std_logic;

-- Reset

display_update_pulse : in std_logic;

-pulse

to update run display

- One

clk_1hz : in std_logic;

hertz clock used to update the timer

button: in std_logic_vector (3 downto 0);

Button press from keypad

pressed : in std_logic;

Pressed from keypad

curr_humidity : in std_logic_vector(15 downto 0);

Current humidity from the sensor

curr_temperature : in std_logic_vector(15 downto 0);

Current temperature from the sensor

Mode: out t_proofer_state;

Current mode of the state machine

Static_Address_Base : out integer range 0 to 2047;

-- Base

address for static display

Dynamic_Address_Base : out integer range 0 to 2047;

-- Base

address for dynamic display

DisplayDataRAM_In : out T_RAM_Port_In;

Display Data Ram

DisplayDataRAM_Out : in T_RAM_Port_Out;

Display Data Ram

RunDataRAM_In : out T_RAM_Port_In;

— Run

Data Ram

RunDataRAM_Out : in T_RAM_Port_Out;

-- Run

Data Ram

buzzer_enable : out std_logic;

Enable the buzzer

active_time : out std_logic_vector(15 downto 0);

Active Time

active_time_remaining : out std_logic_vector(15 downto 0); --

Remaining time for the run

active_temp : out std_logic_vector(15 downto 0);

Active Temperature

active_humid : out std_logic_vector(15 downto 0);

Active Humidity

active_stage : out std_logic_vector(15 downto 0);

Active stage

run_enable : out std_logic

-- Is

```

```

the device running?

);

end Proofing_State;

architecture Behavioral of Proofing_State is

component bcd_2_bin

Port (

bcd_in : in t_bcd;

bin_out : out STDLOGIC_VECTOR (15 downto 0) := (others => '0')

end component;

component DoubleDabble

port (

bin_in : in std_logic_vector (15 downto 0);

bcd_out : out t_bcd

);

end component;

signal current_state : t_proofer_state := main;

- Signals to create a single pulse when a button is first pressed.

signal previous_pressed : std_logic := '0';

signal pulse : std_logic := '0';

- Return state for subprocess.

-- Allows for "calls" to be made in the state machine

signal return_state : t_proofer_state;

- Addresses used for accessing the display data ram and the run data ram

signal current_display_data_address: integer range 0 to 2047;

signal base_display_data_address: integer range 0 to 2047;

signal current_run_data_address : integer range 0 to 2047;

signal base_run_data_address : integer range 0 to 2047;

-- Number conversion signals

signal bcd_2_bin_bcd : t_bcd;

signal bcd_2_bin_bin : std_logic_vector(15 downto 0);

signal dd_bcd : t_bcd;

signal dd_bin : std_logic_vector(15 downto 0);

signal bcd_index : integer range 0 to 5;

signal bin_index : integer range 0 to 1;

-- Signals for run state

signal run_sub_counter : integer range 0 to 31;

signal run_time : std_logic_vector(15 downto 0);

signal run_time_remaining : std_logic_vector(15 downto 0);

signal run_temp : std_logic_vector(15 downto 0);

signal run_humid : std_logic_vector(15 downto 0);

signal run_leading : std_logic;

signal run_stage : std_logic_vector(15 downto 0);

```

```

begin

- Component used to convert bcd a number into a binary number

convert_bcd : bcd_2_bin

Port map(

bcd_{in} \Rightarrow bcd_{2}bin_{bcd},

bin_out \implies bcd_2_bin_bin

);

dd : DoubleDabble

port map (

bin_in \Rightarrow dd_bin,

bcd_out \Rightarrow dd_bcd

);

-- Send out the current mode

Mode <= current_state;

- Send out the current run stage

active_stage <= run_stage;

-- Enable the buzzer when the state is alert

buzzer_enable <= '1' when current_state = alert else '0';

-- Main state machine

state : process (clk, reset_n)

-- Temporary variable to aid in conversion

variable tmp : std_logic_vector(7 downto 0);

- Counter for the timer

variable minute_count : integer range 0 to 255 := 0;

begin

- Reset state for the state machine

if (reset_n = '0') then

current_state <= main;

DisplayDataRAM_In.EN <= '0';

RunDataRAM_In.EN <= '0';

current_run_data_address <= 0;</pre>

base_run_data_address <= 0;

run_enable <= '0';

- On the clock preforms actions.

elsif(rising_edge(clk)) then

case (current_state) is

-- Main state displays the welcome page

when main \Rightarrow

current_run_data_address <= 0;</pre>

base_run_data_address <= 0;

Static_Address_Base <= Const_RAM.main;

Dynamic_Address_Base <= Proc_RAM.main;

if pulse = '1' then

current_state <= enter_time;</pre>

end if;

-- Setup the memory addressed for entering time then run sub-

```

```

routine

when enter_time =>

Static_Address_Base <= Const_RAM.enter_time;

Dynamic_Address_Base <= Proc_RAM.enter_time;</pre>

return_state <= enter_temp;

current_state <= h_data_add_subprocess_setup;</pre>

base_display_data_address <= Proc_RAM.enter_time;

-- Setup the memory addressed for entering temp then run sub-

routine

when enter_temp =>

Static_Address_Base <= Const_RAM.enter_temp;

Dynamic_Address_Base <= Proc_RAM.enter_temp;

return_state <= enter_humid;</pre>

current_state <= h_data_add_subprocess_setup;</pre>

base_display_data_address <= Proc_RAM.enter_temp;

-- Setup the memory addressed for entering humidity then run

sub-routine

when enter_humid =>

Static_Address_Base <= Const_RAM.enter_humid;

Dynamic_Address_Base <= Proc_RAM.enter_humid;</pre>

return_state <= next_point;

current_state <= h_data_add_subprocess_setup;</pre>

base_display_data_address <= Proc_RAM.enter_humid;

-- Prompt the user to see if there is another step in the

proofing run

when next-point =>

Static_Address_Base <= Const_RAM.next_point;

Dynamic_Address_Base <= Proc_RAM.next_point;</pre>

if pulse = '1' then

case (button) is

-- If 'a' is pressed then add another data point

when x"a" \Rightarrow

current_state <= h_display_ram_clear_setup;</pre>

-- If 'b' is pressed then move on to the run state

when x"b" \Rightarrow

current_state <= run_setup;

when others =>

null:

end case;

end if;

- Setup values for reading run

when run_setup =>

Static_Address_Base <= Const_RAM.run;

Dynamic_Address_Base <= Proc_RAM.run;

base_display_data_address <= Proc_RAM.run;

base_run_data_address <= 0;

run_sub_counter <= 0:

current_state <= run_read_time;</pre>

run_stage <= x"0001";

```

```

-- Read in the active time

when run_read_time =>

- reset the minute counter

minute\_count := 0;

run_sub_counter <= run_sub_counter + 1;

case (run_sub_counter) is

when 0 \Rightarrow

current_run_data_address <= base_run_data_address;</pre>

RunDataRAM_In.EN <= '1';

RunDataRAM_In.WE \le '0':

RunDataRAM_In.ADDR <= std_logic_vector(to_unsigned

(base_run_data_address, 11));

when 2 \Rightarrow

run_time <= x"00" & RunDataRAM_Out.DO;</pre>

current_run_data_address <=

current_run_data_address + 1;

RunDataRAM_In.ADDR <= std_logic_vector(to_unsigned

(current_run_data_address + 1,11));

when 4 \Rightarrow

run_time <= RunDataRAM_Out.DO & run_time (7 downto

(0):

current_run_data_address <=

current_run_data_address + 1;

RunDataRAM_In.ADDR <= std_logic_vector(to_unsigned

(current_run_data_address + 1,11));

when 5 \Rightarrow

if (run\_time = x"0000") then

current_state <= alert;

run_stage <= x"0000";

end if;

when 6 \Rightarrow

current_state <= run_read_temp;</pre>

run_sub_counter <= 0;

run_time_remaining <= run_time;

when others =>

null;

end case;

- Read in the active temperature

when run_read_temp =>

run_sub_counter <= run_sub_counter + 1;

case (run_sub_counter) is

when 0 \Rightarrow

run_temp <= x"00" & RunDataRAM_Out.DO;

current_run_data_address <=

current_run_data_address + 1;

RunDataRAM_In.ADDR <= std_logic_vector(to_unsigned

(current_run_data_address + 1,11));

when 2 \Rightarrow

run_temp <= RunDataRAM_Out.DO & run_temp (7 downto

(0):

current_run_data_address <=

current_run_data_address + 1;

RunDataRAM_In.ADDR <= std_logic_vector(to_unsigned

```

```

(current_run_data_address + 1,11));

when 3 \Rightarrow

current_state <= run_read_humid;</pre>

run_sub_counter <= 0;

when others =>

null:

end case;

-- Read in the active humidity

when run_read_humid =>

run_sub_counter <= run_sub_counter + 1;</pre>

case (run_sub_counter) is